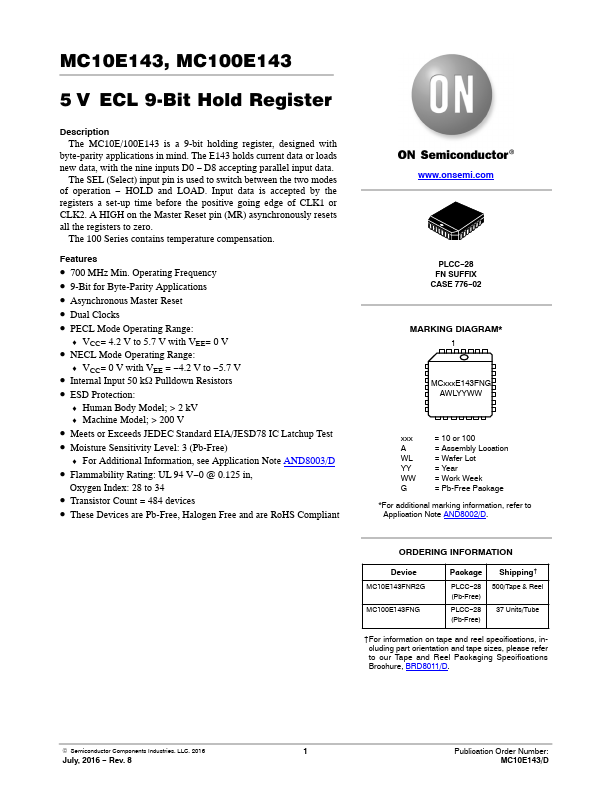

MC10E143

Overview

- 700 MHz Min. Operating Frequency

- 9-Bit for Byte-Parity Applications

- Asynchronous Master Reset

- Dual Clocks

- PECL Mode Operating Range:

- VCC= 4.2 V to 5.7 V with VEE= 0 V

- NECL Mode Operating Range:

- VCC= 0 V with VEE = -4.2 V to -5.7 V

- Internal Input 50 kW Pulldown Resistors

- ESD Protection: